其實,Exynos 4412的IROM代碼已經設置了PLL,我們可以通過串口把IROM設置的PLL寄存器值打印出來,這些值打印出來是這樣的(摘自韋東山老師的《嵌入式Linux系統開發完全手冊_基于4412__上冊》):

CLK_SRC_CPU = 0x01000001

CLK_DIV_DMC0 = 0x00111713

CLK_DIV_DMC1 = 0x01011171

CLK_SRC_TOP0 = 0x01110000

CLK_SRC_TOP1 = 0x00001000

CLK_DIV_TOP = 0x00015470

CLK_SRC_LEFTBUS = 0x00000001

CLK_DIV_LEFTBUS = 0x00000013

CLK_SRC_RIGHTBUS = 0x00000001

CLK_DIV_RIGHTBUS = 0x00000013

APLL_LOCK = 0x00000960

MPLL_LOCK = 0x00000000

EPLL_LOCK = 0x00000FFF

VPLL_LOCK = 0x00000FFF

CLK_DIV_CPU0 = 0x00773730

CLK_DIV_CPU1 = 0x00000077

APLL_CON1 = 0x00003800

APLL_CON0 = 0xA0640301

MPLL_CON1 = 0x00003800

MPLL_CON0 = 0xA0640301

EPLL_CON2 = 0x00000080

EPLL_CON1 = 0x66010000

EPLL_CON0 = 0x00600302

VPLL_CON2 = 0x00000080

VPLL_CON1 = 0x66016000

VPLL_CON0 = 0x006F0302

CLK_SRC_CPU = 0x01000001

CLK_SRC_DMC = 0x00111000

CLK_SRC_TOP0 = 0x01110000

CLK_SRC_TOP1 = 0x00001000

現在來計算 ARMCLK的時鐘頻率:

由上一節《Exynos4412時鐘體系分析》的介紹我們知道,ARMCLK 有如下計算公式:

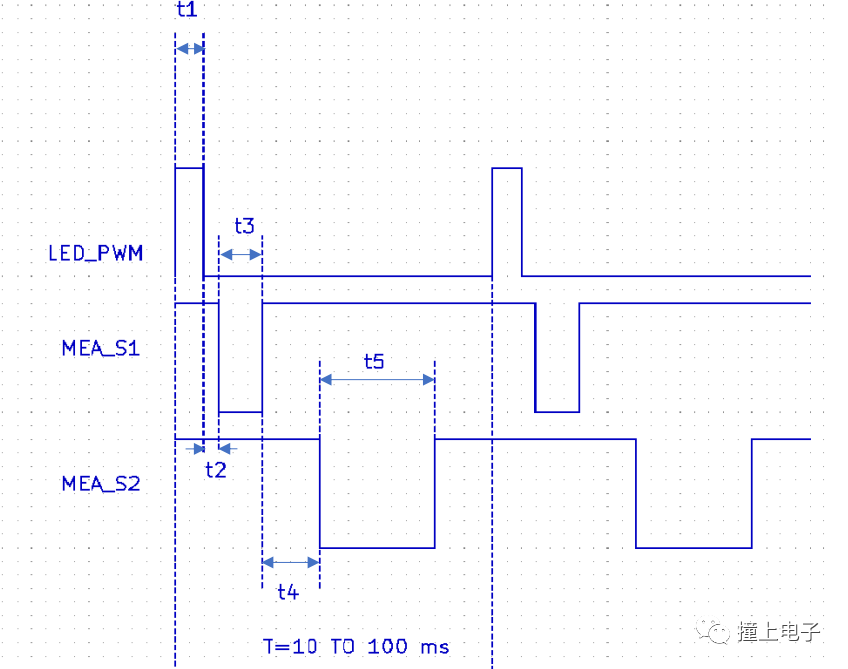

如下圖所示:

由上邊打印的寄存器CLK_SRC_CPU 的值為:

十六進制:0x01000001

二進制:0000 0001 0000 0000 0000 0000 0000 0001

BIT[0] 控制第1個MUX (即 MUXAPLL) ,該位值為1.

BIT[16]控制 第2個 MUX( 即MUXCORE) ,該位值為0.

所以由此看出ARMCLK時鐘走的是如下的路線:

所以:ARMCLK = MUXCORE的輸出 / DIVCORE / DIVCORE2

ARMCLK = MDIV x FIN / (PDIV x 2 ^ SDIV) / (CORE_RATIO + 1) / (CORE2_RATIO + 1)

= 0x64 x 24MHz / (3 x 2 ^ 1) / (0 + 1) / (0 + 1)

= 400 MHz

本次實驗涉及3個小實驗:

system_clock_disable_apll:不使用 APLL,讓CPU運行于 24MHz 頻率,觀察 LED 閃爍是否變慢

system_clock_apll:重新設置APLL,讓 CPU 運行于1.4GHz頻率,觀察 LED 閃爍是否變快

system_clock_plls:參考廠家提供的u-boot代碼,設置所有PLL供后續章節使用第一個小實驗

實現的目標:不使用 APLL,讓CPU運行于 24MHz 頻率,觀察 LED 閃爍是否變慢

一、程序說明

我們在前一個實驗,《Tiny4412之C語言實現流水燈》的基礎上修改。

start.S大部分相同,只是增加一條函數調用語句

bl system_clock_init // 調用時鐘初始化函數

如下圖所示:

鏈接腳本system_clock.lds的內容和上一個實驗key.lds完全相同,只把名字改了改;Makefile的內容也大部分一樣,也只是改了改里邊文件的名字,led.c文件和LED實驗時完全相同,新增加了文件system_clock.c,代碼如下:

/* CMU_CPU */

#define CLK_SRC_CPU (*(volatile unsigned int *)0x10044200)

#define CLK_DIV_CPU0 (*(volatile unsigned int *)0x10044500)

#define CLK_DIV_CPU1 (*(volatile unsigned int *)0x10044504)

/* CMU_DMC */

#define CLK_SRC_DMC (*(volatile unsigned int *)0x10040200)

#define CLK_DIV_DMC0 (*(volatile unsigned int *)0x10040500)

#define CLK_DIV_DMC1 (*(volatile unsigned int *)0x10040504)

/* CMU_TOP */

#define CLK_SRC_TOP0 (*(volatile unsigned int *)0x1003C210)

#define CLK_SRC_TOP1 (*(volatile unsigned int *)0x1003C214)

#define CLK_DIV_TOP (*(volatile unsigned int *)0x1003C510)

/* CMU_LEFTBUS */

#define CLK_SRC_LEFTBUS (*(volatile unsigned int *)0x10034200)

#define CLK_DIV_LEFTBUS (*(volatile unsigned int *)0x10034500)

/* CMU_RIGHTBUS */

#define CLK_SRC_RIGHTBUS (*(volatile unsigned int *)0x10038200)

#define CLK_DIV_RIGHTBUS (*(volatile unsigned int *)0x10038500)

/* locktime */

#define APLL_LOCK (*(volatile unsigned int *)0x10044000)

#define MPLL_LOCK (*(volatile unsigned int *)0x10044008)

#define EPLL_LOCK (*(volatile unsigned int *)0x1003C010)

#define VPLL_LOCK (*(volatile unsigned int *)0x1003C020)

/* APLL */

#define APLL_CON1 (*(volatile unsigned int *)0x10044104)

#define APLL_CON0 (*(volatile unsigned int *)0x10044100)

/* MPLL */

#define MPLL_CON0 (*(volatile unsigned int *)0x10040108)

#define MPLL_CON1 (*(volatile unsigned int *)0x1004010c)

/* EPLL */

#define EPLL_CON2 (*(volatile unsigned int *)0x1003C118)

#define EPLL_CON1 (*(volatile unsigned int *)0x1003C114)

#define EPLL_CON0 (*(volatile unsigned int *)0x1003C110)

/* VPLL */

#define VPLL_CON0 (*(volatile unsigned int *)0x1003C120)

#define VPLL_CON1 (*(volatile unsigned int *)0x1003C124)

#define VPLL_CON2 (*(volatile unsigned int *)0x1003C128)

/*

* 函數名:

* system_clock_init

* 功能: 初始化4412的系統時鐘

*/

void system_clock_init(void)

{

/* IROM或BL1設置了APLL,

* 本程序設置不啟動APLL,

* 而是使在晶振時鐘, 以體驗一下LED閃燈變慢

*/

CLK_SRC_CPU = 0x0;

}

沒什么可說的,很簡單,前部分是后期會用到的一些寄存器地址的定義,主要的是下邊system_clock_init這個函數,在這個函數中將CLK_SRC_CPU寄存器的值設為0,這樣ARMCLK的頻率將走下面這條路徑,設置為24MHZ:

二、編譯、燒寫實驗

按照前幾節介紹的方法,將程序上傳到服務器編譯,并燒寫到SD卡上,給開發板上電,可以明顯感覺到LED閃爍的頻率大大降低,說明我們設置的時鐘起作用了,這里就不上圖了(上了圖大家也看不出來)。

第二個小實驗

實現的目標:重新設置APLL,讓 CPU 運行于1.4GHz頻率,觀察 LED 閃爍是否變快

一、程序說明

文件同第一個小實驗,只是在它的基礎上對system_clock.c文件中的system_clock_init函數進行修改:

/*

* 函數名: system_clock_init

* 功 能: 初始化4412的系統時鐘

* 最終結果: APLL=1.4GHz

*/

void system_clock_init(void)

{

/*

* 1. 在設置APLL之前, 先設置時鐘源為晶振

*/

CLK_SRC_CPU = 0x0;

/*

* 2. 設置APLL

*/

/* 2.1 設置鎖定時間: APLL_CON0中PDIV=3, 所以APLL_LOCK = 270x3 */

APLL_LOCK = 270 * 3;

/* 2.2 設置分頻參數 */

/*

* CORE2_RATIO = 0;

* APLL_RATIO = 2;

* PCLK_DBG_RATIO = 1;

* ATB_RATIO = 6;

* PERIPH_RATIO = 7;

* COREM1_RATIO = 7;

* COREM0_RATIO = 3;

* CORE_RATIO = 0;

*/

CLK_DIV_CPU0 = ((0<<28) | (2<<24) | (1<<20) | (6<<16) | (7<<12) | (7<<8) | (3<<4) | 0);

/*

* CORES_RATIO = 5;

* HPM_RATIO = 0;

* COPY_RATIO = 6;

*/

CLK_DIV_CPU1 = ((5 << 8) |(0 << 4) | (6));

/* 2.3 設置控制參數并使能PLL */

/* 默認值 */

APLL_CON1 = 0x00803800;

/*

* 設置APLL的M,P,S值, APLL輸出 = 0xAF x 24MHz / (3 x 2 ^ 0) = 1.4GHz

* 使能APLL

*/

APLL_CON0 = (1<<31 | 0xAF<<16 | 3<<8 | 0x0);

/* 3. 設置MUX, 使用APLL的輸出 */

CLK_SRC_CPU = 0x01000001;

}

注釋的已經很清楚了,需要注意的就是:上電之后 IROM設置了APLL ,CPU工作于APLL提供的時鐘;當我們要改變 APLL時,要先使得CPU工作于另一個時鐘源,即晶振。設置完APLL后,再讓CPU重新工作于APLL提供的時鐘。

二、編譯、燒寫實驗

按照前幾節介紹的方法,將程序上傳到服務器編譯,并燒寫到SD卡上,給開發板上電,可以明顯感覺到LED閃爍的頻率大大提高(比《Tiny4412之C語言實現流水燈》時閃爍的還要快,因為當時CPU運行在400MHZ,現在運行在1.4GHZ),說明我們設置的時鐘起作用了,這里就不上圖了(上了圖大家也看不出來)。

第三個小實驗

實現的目標:參考廠家提供的u-boot代碼,設置所有PLL供后續章節使用

一、程序說明

文件同第一個小實驗,只是在它的基礎上對system_clock.c文件中的system_clock_init函數進行修改:

/*

函數名:

system_clock_init

功能:

初始化4412的系統時鐘

最終結果:

A=1400000000, M=800000000, E=96000000 V=350000000

ARMCLK=1500000000, DMC=400000000, ACLK200=160000000

ACLK100=100000000, ACLK160=160000000, ACLK133=133333333

*/

void system_clock_init(void)

{

/* 1.設置CMU_CPU相關 */

CLK_SRC_CPU = 0x0; // 設置CMU_CPU部分中所有的MUX的源

/* 2.設置CMU_DMC相關 */

/*

CORE_TIMERS_RATIO = 0x0;

COPY2_RATIO = 0x0;

DMCP_RATIO = 0x1;

DMCD_RATIO = 0x1;

DMC_RATIO = 0x1;

DPHY_RATIO = 0x1;

ACP_PCLK_RATIO = 0x1;

ACP_RATIO = 0x3;

*/

CLK_DIV_DMC0 = ((0x0 << 28) | (0x0 << 24) | (0x1 << 20) | (0x1 << 16) | (0x1 << 12) | (0x1 << 8) | (0x1 << 4) | (0x3));

CLK_DIV_DMC1 = 0x07071713;

/* 3.設置CMU_TOP相關 */

/*

MUX_ONENAND_SEL = 0x0;

MUX_ACLK_133_SEL = 0x0;

MUX_ACLK_160_SEL = 0x0;

MUX_ACLK_100_SEL = 0x0;

MUX_ACLK_200_SEL = 0x0;

MUX_VPLL_SEL = 0x1;

MUX_EPLL_SEL = 0x1;

*/

CLK_SRC_TOP0 = ((0x0 << 28) | (0x0 << 24) | (0x0 << 20) | (0x0 << 16) | (0x0 << 12) | (0x1 << 8) | (0x1 << 4));

CLK_SRC_TOP1 = 0x01111000;

/*

ACLK_400_MCUISP_RATIO = 0x1;

ACLK_266_GPS_RATIO = 0x2;

ONENAND_RATIO = 0x1;

ACLK_133_RATIO = 0x5;

ACLK_160_RATIO = 0x4;

ACLK_100_RATIO = 0x7;

ACLK_200_RATIO = 0x4;

*/

CLK_DIV_TOP = ((0x1 << 24) | (0x2 << 20) | (0x1 << 16) | (0x5 << 12) | (0x4 << 8) | (0x7 << 4) | (0x4));

/* 3.設置CMU_LEFTBUS相關 */

CLK_SRC_LEFTBUS = 0x10;

/*

GPL_RATIO = 0x1;

GDL_RATIO = 0x3;

*/

CLK_DIV_LEFTBUS = ((0x1 << 4) | (0x3));

/* 4.設置CMU_RIGHTBUS相關 */

CLK_SRC_RIGHTBUS = 0x10;

/*

GPR_RATIO = 0x1;

GDR_RATIO = 0x3;

*/

CLK_DIV_RIGHTBUS = ((0x1 << 4) | (0x3));

/* 5.設置各個鎖相環(PLL)的locktime */

APLL_LOCK = (0x3 * 270);

MPLL_LOCK = (0x3 * 270);

EPLL_LOCK = (0x2 * 3000);

VPLL_LOCK = (0x2 * 3000);

/*

APLL_RATIO = 0x2;

CORE_RATIO = 0x0;

CORE2_RATIO = 0x0;

COREM0_RATIO = 0x3;

COREM1_RATIO = 0x7;

PERIPH_RATIO = 0x7;

ATB_RATIO = 0x6;

PCLK_DBG_RATIO = 0x1;

*/

CLK_DIV_CPU0 = ((0x0 << 28) | (0x2 << 24) | (0x1 << 20) | (0x6 << 16) | (0x7 <<12) | (0x7 << 8) | (0x3 << 4) | (0x0));

/*

CORES_RATIO = 0x5;

HPM_RATIO = 0x0;

COPY_RATIO = 0x6;

*/

CLK_DIV_CPU1 = ((0x5 << 8) |(0x0 << 4) | (0x6));

/* 6.設置APLL = 1400000000 */

APLL_CON1 = 0x00803800;

APLL_CON0 = (1<<31 | 0xAF<<16 | 0x3<<8 | 0x0);

/* 7.設置MPLL = 800000000 */

MPLL_CON1 = 0x00803800;

MPLL_CON0 = (1<<31 | 0x64<<16 | 0x3<<8 | 0x0);

/* 8.設置EPLL = 96000000 */

EPLL_CON2 = 0x00000080;

EPLL_CON1 = 0x66010000;

EPLL_CON0 = (1<<31 | 0x40<<16 | 0x2<<8 | 0x3);

/* 9.設置VPLL = 350000000 */

VPLL_CON2 = 0x00000080;

VPLL_CON1 = 0x66010000;

VPLL_CON0 = (1<<31 | 0x48<<16 | 0x2<<8 | 0x3);

/*10.修改源*/

CLK_SRC_CPU = 0x01000001;

CLK_SRC_DMC = 0x00011000;

CLK_SRC_TOP0 = 0x00000110;

CLK_SRC_TOP1 = 0x01111000;

}

二、編譯、燒寫實驗

按照前幾節介紹的方法,將程序上傳到服務器編譯,并燒寫到SD卡上,給開發板上電,現象和第二個小實驗完全相同。

上一篇:TINY4412裸機程序,按鍵檢測

下一篇:tiny4412 裸機程序 一、說明

推薦閱讀

史海拾趣

隨著公司規模的不斷擴大,ABL Heatsink開始重視品牌建設和市場推廣。公司加大了在廣告、展會等方面的投入,提升了品牌知名度。同時,ABL Heatsink還積極參與行業交流活動,與同行分享經驗和技術,進一步鞏固了公司的行業地位。

ABL Heatsink公司在發展過程中,積極尋求與其他企業的合作。通過與芯片制造商、電子設備生產商等建立緊密的合作關系,ABL Heatsink成功將自己的散熱器產品集成到各種高端電子設備中。這種合作模式不僅提升了公司的知名度,也帶來了穩定的訂單和收入。

在BERNSTEIN公司的發展過程中,家族傳承和企業管理一直是一個重要的主題。Hans-Joachim Bernstein作為Hans Bernstein的長子,在塑造公司的成功故事中發揮了重要作用。在他的管理下,“SpezialFabrik für Schaltkontakte”公司發展成為當今在國際上活躍的技術集團。這家家族企業現已進入第三代,Nicole和Achim Bernstein作為新一代領導人,繼續傳承著家族的優良傳統和企業文化,推動著公司的持續發展。

2012年,展恒電子與FANSO(孚安特)簽訂戰略合作協議,共同向智能電表廠家提供配套銷售服務。這一合作不僅拓寬了展恒電子的銷售渠道,也提升了公司在智能電表市場的影響力。此后,展恒電子繼續與多家知名企業建立戰略合作關系,通過資源共享和優勢互補,實現了共贏發展。

EBG RESISTORS LLC公司成立于XXXX年,由幾位電子工程師共同創立。初創時期,公司面臨著資金短缺、市場競爭激烈等多重挑戰。然而,創始人們憑借對電阻器技術的深厚理解和熱情,堅持研發高質量、高性能的電阻器產品。他們夜以繼日地工作,不斷優化產品設計和生產工藝,終于在市場上贏得了客戶的認可。

|

搞了近二星期, 終于看到6.0的桌面了, 也就是說我的OAL部分和LCD驅動部分已移植成功. 板子是優龍的FS2410, 原來提供的是5.0的BSP. 用的還是4.2的目錄結構, 移植過程那就一痛苦. 我的方法是先clone的一個6.0的自帶的BSP, 用的是DEVICEEMULATOR. 我 ...… 查看全部問答∨ |

|

|

請教高手,同一板子上有兩個不同版本的BSP,A版的EBOOT.NB0和EBOOT.BIN都是好的,B版要用A版的EBOOT.NB0燒B版的EBOOT.BIN,EBOOT才能起來,也就是說,為什么用B版的EBOOT.NB0燒B版的EBOOT.BIN后,EBOOT起不來,EBOOT.BIN又沒有問題,請問高手是什么 ...… 查看全部問答∨ |

|

|

如圖片,這是我的芯片的I2C的地址說明。我讓芯片作為從,主機(STM32的I2C2)作為主。上面說了可以用:通用地址:0000000或者11XXXXHW,我把HW接高電平了,HW=1.但是我試遍了11XXXX1,主機都得不到ACK,用0000000曾經試通過,并且讀到信息。現在 ...… 查看全部問答∨ |

設計資源 培訓 開發板 精華推薦

- 試用Vishay新型“IHLP磁芯損耗計算器”,搶樓贏好禮

- LPC4370重磅來襲 有獎問答贏好禮!

- 電子工程師,如何更好地擁抱GaN?參與問卷有好禮!

- 報名贏京東卡 | 國產FPGA安路科技2024線上新品發布會

- 兆易GD32450I-EVAL免費測評試用

- 追更有驚喜:解救被FSM折磨過的你,justd0解析LSM6DSOX有限狀態機官方例程

- 電路圖站2.0版上線,公開征集網友建議,填寫調查問卷贏積分!

- 全球首款Cortex-M23內核物聯網芯片SAML10和SAM L11系列 闖關獲取SAML10/SAML11法寶,拆除電子界安全危機,贏好禮!

- 邀請好友體驗WEBENCH,禮品豐厚你有他也有!

A500LN

A500LN

京公網安備 11010802033920號

京公網安備 11010802033920號