RAM的原理簡單學習

DDR是RAM的一種,RAM常見的類型有SRAM,SDRAM,DDR他們的共同特點是,隨機存儲意味著讀寫速度快,掉電后數(shù)據(jù)丟失,所以常用來存儲程序中的變量。

SRAM

靜態(tài)隨機存儲器英文是static random-access memory 就是保持上電就可以保存數(shù)據(jù)而不需要刷新。數(shù)據(jù)線和地址線分離以IS62WV51216這個芯片為例,他數(shù)據(jù)位寬為16,大小為1MB,地址線寬是19。所以可以訪問的空間大小就是2的19次方即524288=512KB,然后數(shù)據(jù)線是16位了,所以512KB*2 就是這個芯片的全部容量。然后在加上一些必要的控制線比如片選,字節(jié)選擇等就可以完成讀寫控制,他的特點是不需要刷新讀寫速度快,但是價格高STM32單片機內部的RAM就是這種的。

SDRAM

同步動態(tài)隨機存儲器英文是 synchronous Dynamic random access memory ,他就是為了解決SRAM的成本高的問題而被發(fā)明出來的,同步則說明SDRAM工作時需要時鐘線,動態(tài)是因為需要不斷的刷新從而避免數(shù)據(jù)丟失。他的特點是集成度高,功耗低,成本低,適合做大容量存儲。他的發(fā)展過程是SDRAM,DDR SDRAM,DDR2 SDRAM,DDR3 SDRAM,DDR4 SDRAM 。同樣本次也找一個芯片來學習,W9825G6KH為例,他是一個16bit位寬的32M的SDRAM,速度常見為200Mhz。SDRAM 的組成就相對復雜一些。

CLK:時鐘

CKE:時鐘使能

CS:片選

RAS;行選通

CAS:列選通

WE:寫勢能

A0-A12:地址線,其中A10比較特殊是預充電:關閉打開的行準備新的行。

BANK:SDRRAM多是由多個bank組成的,常見由2,4,8等,當前新有4個bank所以他有兩個bank選擇線BS0和BS1.

D0-D15:數(shù)據(jù)線

U/L DQM:高低字節(jié)選擇,如果數(shù)據(jù)線是8bit寬就不需要。

DDR就是SDRAM的升級版本,工作原理相同,但不僅在時鐘頻率上提高,而寫在一個時鐘周期傳輸兩次數(shù)據(jù)即上升沿和下降沿都傳輸數(shù)據(jù)。這就是預取2bit隨著技術的發(fā)展預取已經(jīng)可以在DDR3的時候做到8bit,所以對于速度的提高是成倍的。這里就不深究其實現(xiàn)原理。

這里主要就其尋址方式進行分析學習一下,同SDRAM一樣DDR也是將地址線分為行和列地址通過行和列宣統(tǒng)信號來決定。就那當前舉例的芯片來說,他講地址線中的全部作為行地址而A0-A8作為列地址,所以可以尋址的空間就是2^13*2^9=4194304=4MB,數(shù)據(jù)位寬為2字節(jié)16bit所以真實可以尋址的空間是8M,然后這個芯片的總存儲容量是32m,所以這里就是bank的作用了,前面的地址線尋址范圍實際上是一個bank的空間,再加上bank選擇線2^2=4 所以最后可以尋址的空間就是8*4 = 32M 的空間了。

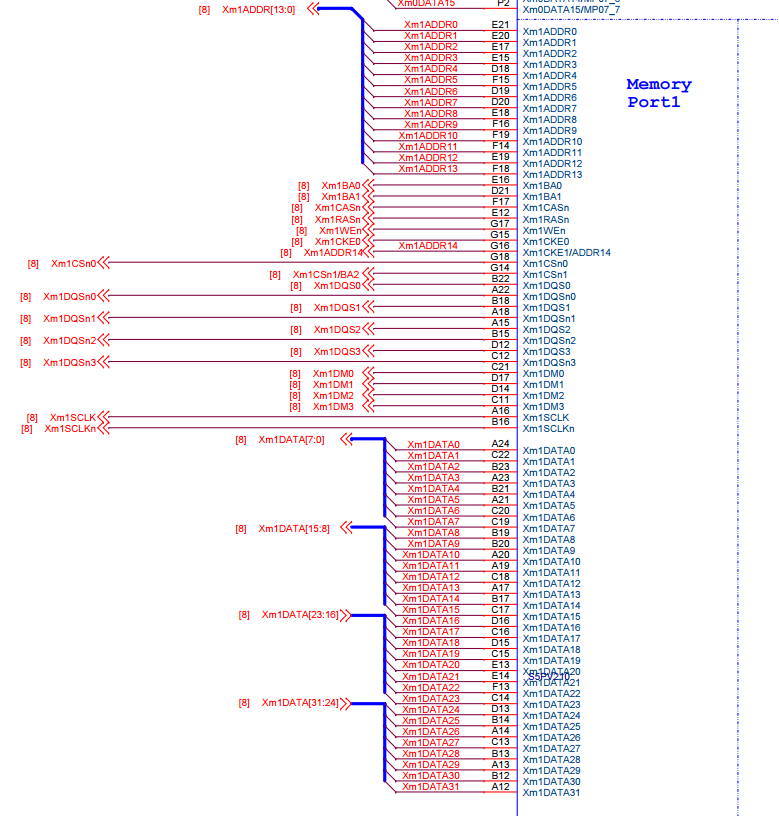

Tiny210 的DDR配置

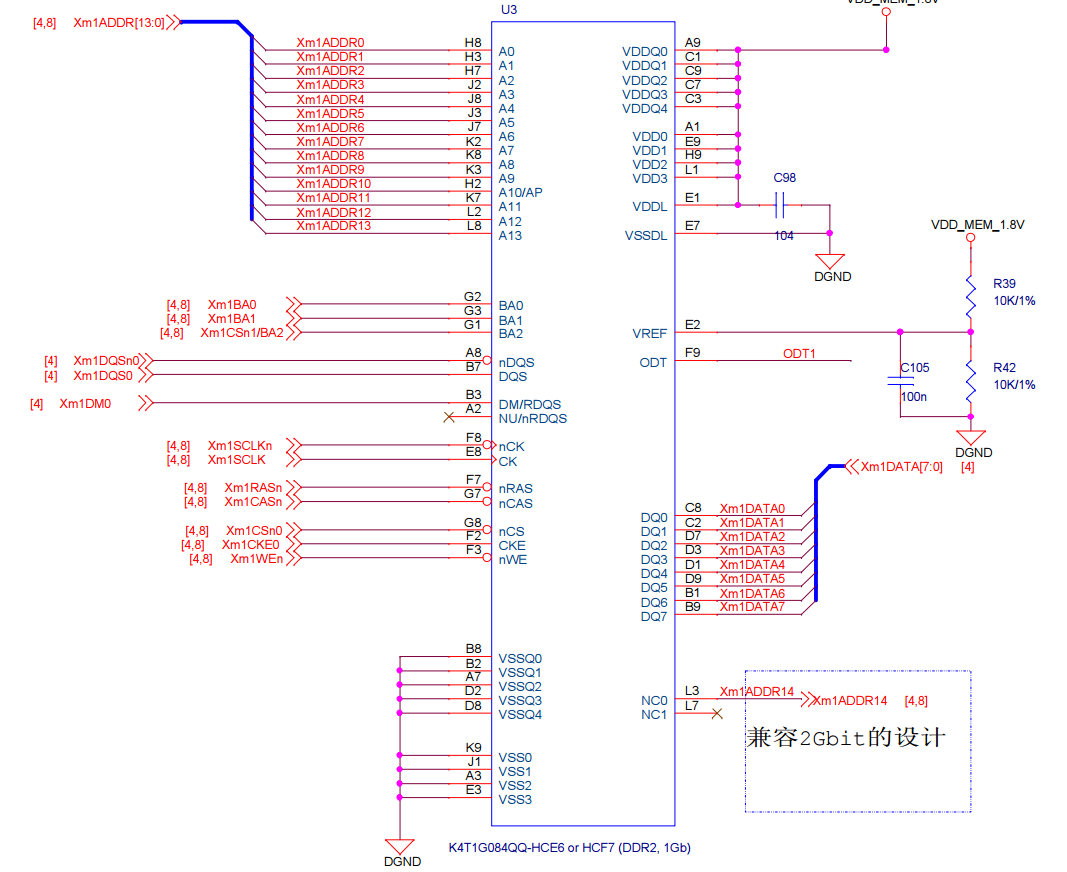

我的板子是一個比較早的友善之臂的tiny210加他自家的TinySDK底板,不過DDR在核心板上所以核心板一樣的原理都一樣。核心板上一共有四顆DDR芯片型號為K4T1G084QQ-HCE6 ,通過查看手冊知道這個芯片的是一個8bank的128M的內存芯片,具體的DDR初始化相關的參數(shù)配置細節(jié)這里不看了,主要看一下DDR的尋址配置。

這個芯片的地址線是A0-A13一共14條地址線其中行地址占全部地址線,列地址為A0-A9共10條,數(shù)據(jù)線寬為8bit。所以通過前面的原理可以知道他的尋址空間是 2^14*2^10*8=134217728就是128Gb所以和芯片的大小剛剛好相同。現(xiàn)在來看友善的電路連接方式:

從圖中可以看到友善采用的方式是將8片的數(shù)據(jù)腳并在一起從而組成一個數(shù)據(jù)位寬為32位的數(shù)據(jù)接口,所以最后地址線的尋址只需要1G/4=128M的尋址空間就可以完成整個板載內存的尋址訪問。現(xiàn)在看來雖然很清晰但是剛開始配置這一塊的時候還是迷茫了幾個小時,最后沒辦法先去簡單看了SDRAM的尋址原理之后在來看這兒就好多了。 首先要排除原理圖中的ADDR14這個的影響,因為這個地址線是預留給2G的硬件的。

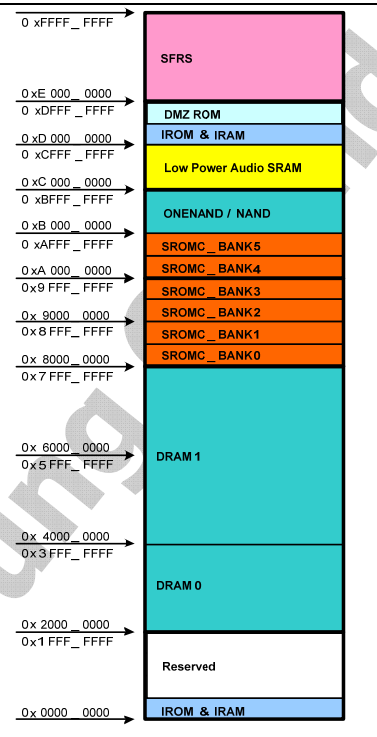

通過芯片這部分的原理圖可以看到,他將DDR芯片的bank腳B2接在了SOC的DDR控制器的片選腳Xm1CSn1/BA2上,而芯片的真正片選腳接在了Xm1CSn0上,所以這樣看來應該是設計把兩種方案,一是將四片DDR準備讓控制器作為兩片256的內存在驅動了,第二是作為一個DDR芯片來驅動此時這個腳就做BA2使用,在我自己調試這一部分時還是花了些時間搞明白這一點的。所以目前對于SOC的DDR控制器而言外部應該是接了32位數(shù)據(jù)位寬的4 bank的DDR芯片兩片或者32位寬的8bank芯片;在DDR控制器看來是這樣的外部的內存應該是數(shù)據(jù)位寬32bit,行地址14bit,列地址10bit,四個bank的芯片2片或者行地址14bit,列地址10bit,八個bank的芯片1片;當作為兩片DDR內存時一個芯片的尋址范圍就是2^14*2^10*4*4=268435456就是256MB,其中第一個4表示有4個bank,而后面的4 因為現(xiàn)在的數(shù)據(jù)線位32bit就是四個字節(jié)了,最后整個個SDRAM 的尋址空間就是256Gx2=512M;其次是 2^14*2^10*4*8 = 536890912即512M。其中第二種就是我目前U-boot的上512GB的DDR的配置方案了。說道這里的吐槽一下友善的DDR的裸機例程太坑了,雖然注釋已經(jīng)寫了提供的歷程不是他們的最后u-boot中的初始化配置方案,但是他的配置代碼由多余的就不說了,還只是初始化了128M的內存空間,一開始以為大小最起碼是正確的可能和他們真正用到u-boot中的初始化比穩(wěn)定性差一點,所以我在移植u-boot時在代碼重定向的地址就超過了128M所以就跑到了未初始化的地址范圍外了,然后直接死掉這個問題查的我好苦最后才發(fā)現(xiàn)是給的DDR例程初始化只能128M內的空間可以正常使用。

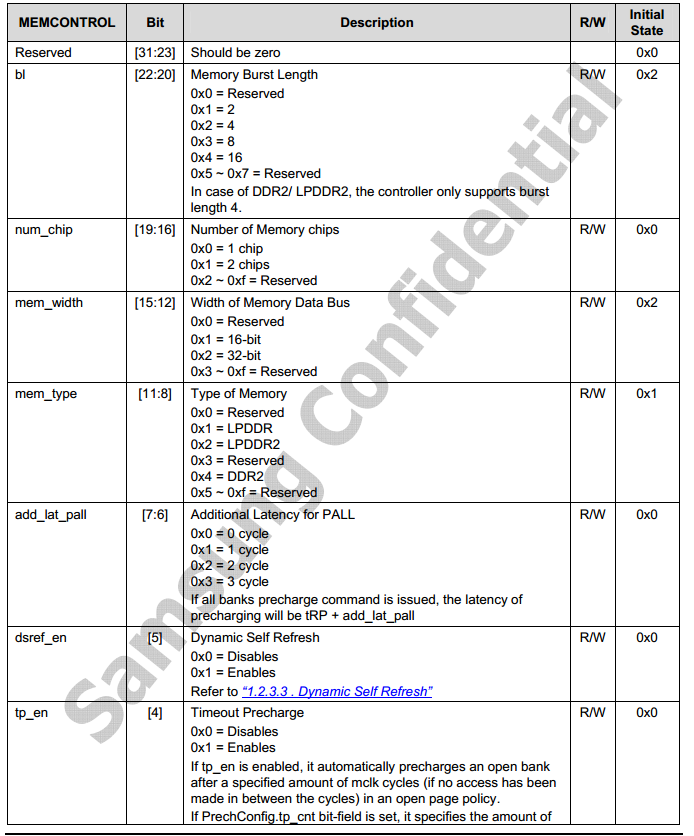

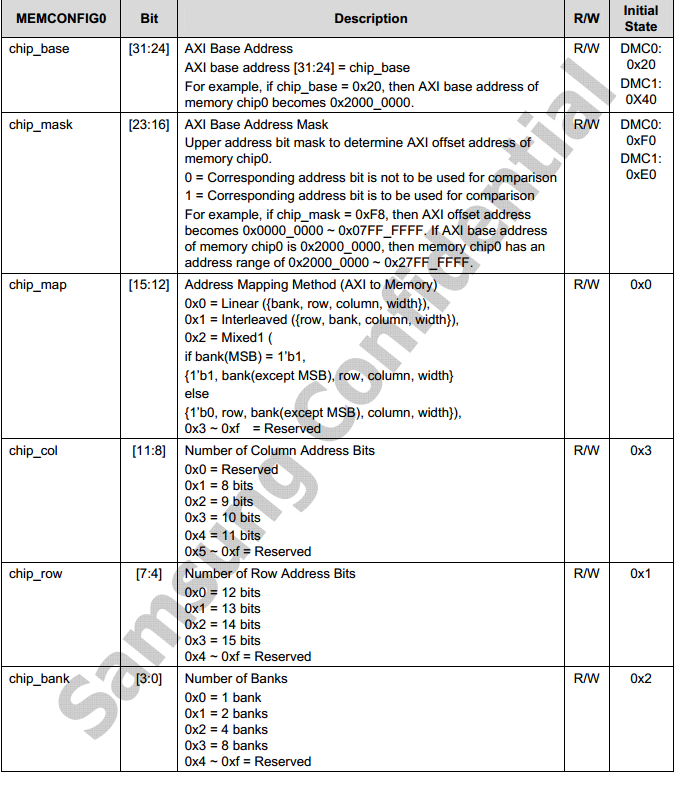

最后來看一下代碼的配置并驗證一下,這里也是只重點看DRAM控制器的配置部分。參考三星的手冊的部分我先在下面貼出來

s5p210_mem_init:

@ 1. DMC0 Drive Strength (Setting 2X)

ldr r0, =S5PC100_GPIO_BASE

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_0DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_1DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_2DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_3DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_4DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_5DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_6DRV_SR_OFFSET]

ldr r1, =0x0000AAAA

str r1, [r0, #MP1_7DRV_SR_OFFSET]

ldr r1, =0x00002AAA

str r1, [r0, #MP1_8DRV_SR_OFFSET]

@ 2. ?????PHY DLL

ldr r0, =APB_DMC_0_BASE

@step 3: PhyControl0 DLL parameter setting, manual 0x00101000

ldr r1, =0x00101000

str r1, [r0, #DMC_PHYCONTROL0]

@PhyControl1 DLL parameter setting, LPDDR/LPDDR2 Case

ldr r1, =0x00000086

str r1, [r0, #DMC_PHYCONTROL1]

@step 2: PhyControl0 DLL on

ldr r1, =0x00101002

str r1, [r0, #DMC_PHYCONTROL0]

@step 4: PhyControl0 DLL start

ldr r1, =0x00101003

str r1, [r0, #DMC_PHYCONTROL0]

find_lock_val:

@Loop until DLL is locked

ldr r1, [r0, #DMC_PHYSTATUS]

and r2, r1, #0x7

cmp r2, #0x7

bne find_lock_val

@Force Value locking

and r1, #0x3fc0

mov r2, r1, LSL #18

orr r2, r2, #0x100000

orr r2 ,r2, #0x1000

orr r1, r2, #0x3

str r1, [r0, #DMC_PHYCONTROL0]

@ 3. ?????DMC0

@step 5: ConControl auto refresh off

ldr r1, =0x0FFF2010

str r1, [r0, #DMC_CONCONTROL]

@step 6: MemControl BL=4, 1 chip, DDR2 type, dynamic self refresh, force precharge, dynamic power down off

@burst 4, num_chip 1 dw=32,type ddr2 ,PALL 0

@ 0x00202400 0x00212400

@以上內容全部是參考網(wǎng)上的三星參考代碼部分初始化的,一下才是我修改的

@解釋:

@最低8個bit的00

@關閉動態(tài)時鐘

@關閉power down 這部分都是降低功耗才會考慮的

@ 4 我的DDR芯片是DDR2

@ 2 前面說了用4個8bit組成了32bit數(shù)據(jù)寬度

@ 0 四片等效成一片 前面也說了

@ 2 根據(jù)手冊只能是2

ldr r1, =0x00202400

str r1, [r0, #DMC_MEMCONTROL]

@step 7: MemConfig0 256MB config, 8 banks,Mapping Method[12:15]0:linear, 1:linterleaved, 2:Mixed

@解釋:

@ 3 前面說了這個型號的DDR是內部由8個bank的

@ 2 row地址寬14

@ 3 col地址寬10

@ 0 線性地址

@ E0 不可用地址空間的掩碼,手冊中說如果你是F8則尋址空間就是0~0x07ffffff 很清楚把,

所以我這里512M就是E0 就是0~0x1fffffff

@ 20 這一片內存的基地址手冊可以看出如果為20則就是0x20000000 所以DMC0上就是剛剛好全部映射20000000~3fffffff

ldr r1, =0x20E00323

str r1, [r0, #DMC_MEMCONFIG0]

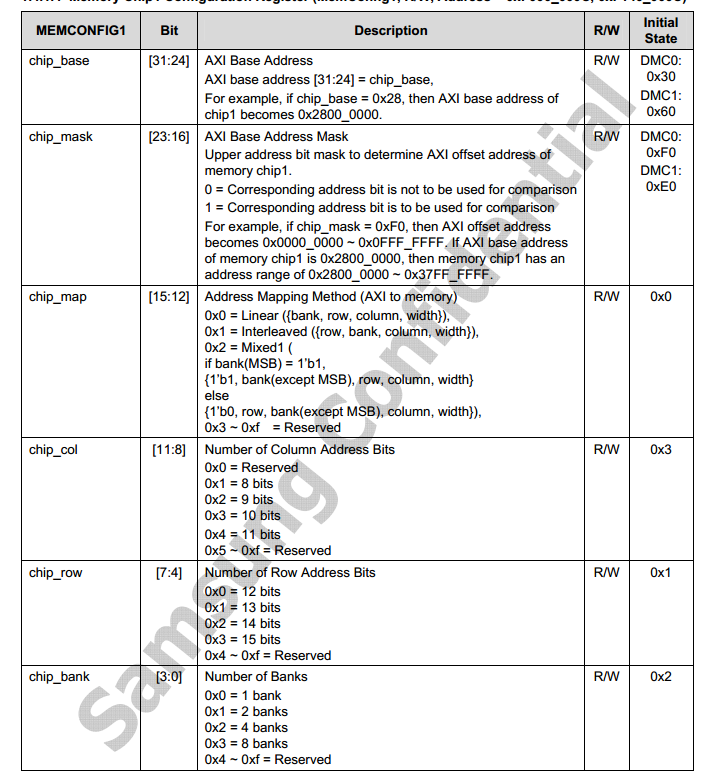

@MemConfig1 如果等效為兩顆芯片,才需要配置第二個芯片

@解釋:

@ 3 前面說了這個型號的DDR是內部由8個bank的,這里卻配置為4個bank其實就是

前面說的他巧用了一條片選線用來作為bank的第三條線

@ 2 row地址寬14

@ 3 col地址寬10

@ 0 線性地址

@ F0 不可用地址空間的掩碼,手冊中說如果你是F8則尋址空間就是0~0x07ffffff 很清楚把,所以我這里256M就是F0

@ 40 這一片內存的基地址手冊可以看出如果為40則就是0x40000000加上我前面就是0x3fffffff 這里就是從RAM1的地址空間開始映射則就是

@ldr r1, =0x40F00323

@str r1, [r0, #DMC_MEMCONFIG1]

@以下內容全部是參考網(wǎng)上的三星參考代碼部分初始化的,一上才是我修改的

@step 8:PrechConfig

ldr r1, =0xFF000000

str r1, [r0, #DMC_PRECHCONFIG]

@step 9:TimingAref 7.8us@133MHz=1038(0x40E), 100MHz=780(0x30C), 20MHz=156(0x9C), 10MHz=78(0x4E)

ldr r1, =DMC0_TIMINGA_REF

str r1, [r0, #DMC_TIMINGAREF]

@TimingRow for @200MHz

ldr r1, =DMC0_TIMING_ROW

str r1, [r0, #DMC_TIMINGROW]

@TimingData CL=4

ldr r1, =DMC0_TIMING_DATA

str r1, [r0, #DMC_TIMINGDATA]

@TimingPower

ldr r1, =DMC0_TIMING_PWR

str r1, [r0, #DMC_TIMINGPOWER]

@ 4.DDR2 DRAM

@DirectCmd chip0 Deselect

ldr r1, =0x07000000

str r1, [r0, #DMC_DIRECTCMD]

@step 16:DirectCmd chip0 PALL

ldr r1, =0x01000000

str r1, [r0, #DMC_DIRECTCMD]

@step 17:DirectCmd chip0 EMRS2

ldr r1, =0x00020000

str r1, [r0, #DMC_DIRECTCMD]

@step 18:DirectCmd chip0 EMRS3

ldr r1, =0x00030000

str r1, [r0, #DMC_DIRECTCMD]

上一篇:u-boot 移植 --->5、友善之臂Tiny210底板王網(wǎng)卡驅動移植

下一篇:u-boot 移植 --->6、引導Linux啟動測試

推薦閱讀最新更新時間:2025-04-06 16:09

設計資源 培訓 開發(fā)板 精華推薦

- 迅為IMX6開發(fā)板Android應用-AndroidStudio-calculator測試

- 玩轉 ESP32 + Arduino (二十) SIM800L上傳數(shù)據(jù)到OneNet(新版Mqtts)

- 玩轉 ESP32 + Arduino (二十一) SPIFFS文件系統(tǒng) (已棄用)

- 玩轉 ESP32 + Arduino (二十二) SIM800L上傳數(shù)據(jù)到阿里IOT(溫濕度和LBS)(NTP對時)

- 玩轉 ESP32 + Arduino (二十三) 多文件系統(tǒng)及全局變量

- 玩轉 ESP32 + Arduino (二十四) SD卡讀寫

- 玩轉 ESP32 + Arduino (二十五) SSD1306庫驅動OLED

- 玩轉 ESP32 + Arduino(二十六) 按鍵控制庫 OneButton

- 玩轉 ESP32 + Arduino(二十七) ESP對象

- 采用 LTM4630 36A VDDQ 電源的 LTM4632IY 4V 至 15V 輸入、2 相單輸出 ±6A VTT 終端設計的典型應用電路

- AN56778, PowerPSoC - 具有集成 LED 驅動器的 MPPT 太陽能充電器

- H743II核心板配套3.5寸IPS電容觸摸屏模塊

- 無線開關-六路

- EVAL-ADM1067LFEB,評估 ADM1067ACP 電壓監(jiān)控器排序器的評估板

- LF50ABPT-TR 5V 多路低壓降穩(wěn)壓器電源的典型應用,帶 ON/OFF 撥動開關

- AR0237CSSC00SUEAD3-GEVK:2 MP Sunex DSL945D 1/3" iBGA CIS DK 評估套件

- NCS214RMUTAGEVB:電流檢測放大器

- ti小車

- 使用 ROHM Semiconductor 的 BD49K26G-TL 的參考設計

C語言高級編程及實例剖析

C語言高級編程及實例剖析 汽車電工電子技術基礎實驗實訓指導書

汽車電工電子技術基礎實驗實訓指導書

京公網(wǎng)安備 11010802033920號

京公網(wǎng)安備 11010802033920號