開發(fā)板:mini2440

內(nèi)核 :linux2.6.32.2

參考 :韋東山畢業(yè)班I2C視頻教程

1、i2c協(xié)議簡要分析

i2c中線是一種由 PHILIPS 公司開發(fā)的串行總線,用于連接微控制器及其外圍設備,它具有以下特點。

1、只有兩條總線線路:一條串行數(shù)據(jù)線SDA,一條串行時鐘線SCL。

2、每個連接到總線的器件都可以使用軟件根據(jù)它的唯一的地址來確定。

3、傳輸數(shù)據(jù)的設備之間是簡單的主從關系。

4、主機可以用作主機發(fā)送器或者主機接收器。

5、它是一個真正的多主機總線,兩個或多個主機同時發(fā)起數(shù)據(jù)傳輸時,可以通過沖突檢測和仲裁來防止數(shù)據(jù)被破壞。

6、串行的8位雙向傳輸,位速在標準模式下可達 100kbit/s,在快速模式下可達400kbit/s,在高速模式下可待3.4Mbit/s。

7、片上的濾波器可以增加抗干擾能力,保證數(shù)據(jù)的完整性。

8、連接到同一總線上的IC數(shù)量只受到總線的最大電容400Pf的限制。

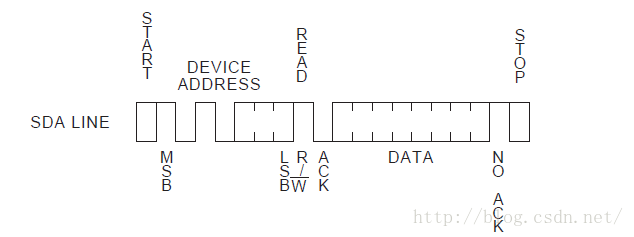

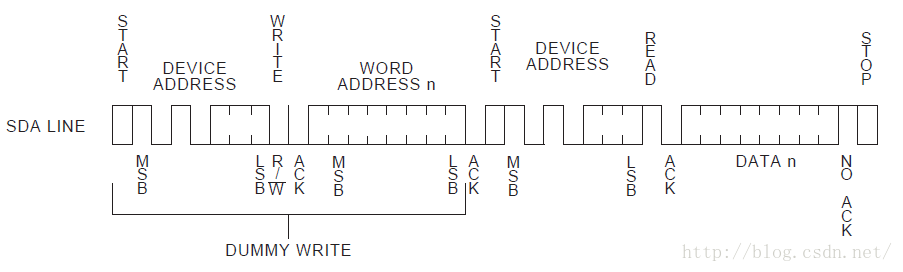

如上圖所示,啟動一個傳輸時,主機先發(fā)送一個S信號,然后發(fā)送8位數(shù)據(jù)。這8位數(shù)據(jù)的前7位為從機地址,第八位表示傳輸?shù)姆较颍?表示寫,1表示讀),如果有數(shù)據(jù)則繼續(xù)發(fā)送,最后發(fā)出P信號停止。

信號類型:

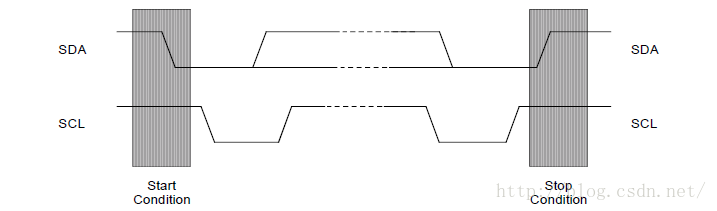

注意:正常數(shù)據(jù)傳輸時,SDA 在 SCL 為低電平時改變,在 SCL 為高電平時保持穩(wěn)定。

開始信號 S 信號:

SCL 為高電平時,SDA由高電平向低電平跳變,開始傳送數(shù)據(jù)。

結束信號 P 信號:

SCL 為高電平時,SDA由低電平向高電平跳變,結束傳送數(shù)據(jù)。

響應信號 ACK:

接收器在接收到8位數(shù)據(jù)后,在第9個時鐘周期,拉低 SDA 電平

注意:在第9個時鐘周期,發(fā)送器保持SDA為高,如果有ACK,那么第9個時鐘周期SDA為低電平,如果沒有為高電平,發(fā)送器根據(jù)電平高低分辨是否有ACK信號。

如果使能了IIC中斷,發(fā)送完8bit數(shù)據(jù)后,主機自動進入中斷處理函數(shù),此時SCL被發(fā)送器拉低,讓接收器被迫等待。恢復傳輸只需要清除中斷掛起。

2、 s3c2440 讀寫流程

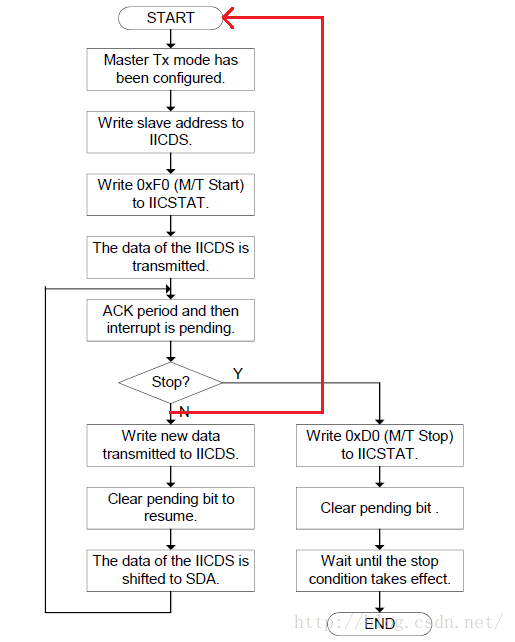

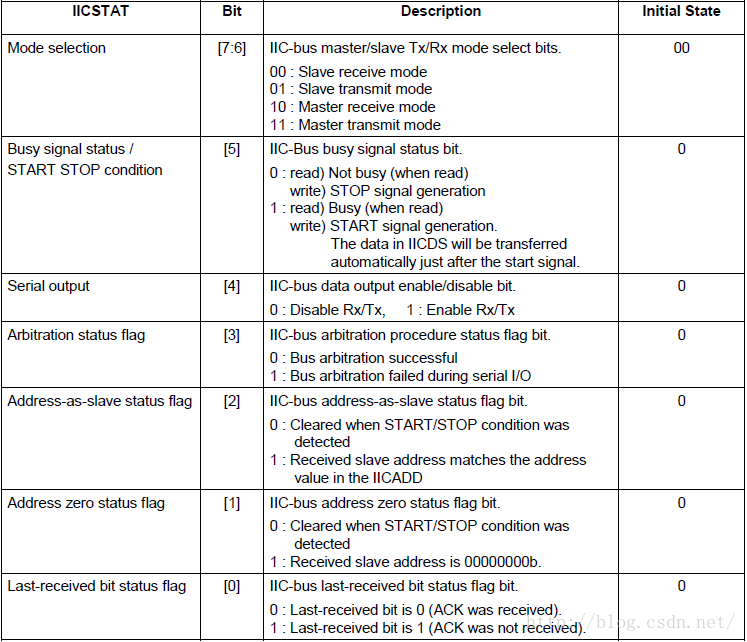

1、設置傳輸模式 IICSTAT[7-6],我們做實驗與AT24C08通信時,2440作為主機,因此只用到主機發(fā)模式和主機收模式。

2、寫入從機地址到 IICDS[7-1],此時IICDS[7-1]位表示從機地址,第0位不關心。如 AT24C08 為 0xA0(最低位寫0了,發(fā)送到數(shù)據(jù)線上的7位地址的后邊以為才表示收發(fā),這里雖然寫0但并不是根據(jù)這里的0來真正發(fā)送的)。

3、寫 0xF0(寫) 或 0xB0(讀)到 IICSTAT 寄存器, 高兩位表示 傳輸模式前邊設置過了,設置IICSTT[5-4] 為 11,使能傳輸,發(fā)送S信號。

4、IIC控制器自動將第2步中設置的 IICDS[7-1] 再根據(jù) 傳輸模式 補充 IICDS[0]位,發(fā)送出去。

5、進入第9個時鐘周期,此時,從機決定是否發(fā)出ACK信號,主機進入中斷,判斷是否收到ACK信號,以及是否繼續(xù)傳輸。

繼續(xù)發(fā)送:

1、將數(shù)據(jù)寫入 IICDS

2、清除中斷掛起,SCL時鐘恢復,IICDS的數(shù)據(jù)被自動發(fā)送到 SDA 線上,回到第5步。

停止發(fā)送:

1、寫 0xD0(寫) 和 0x90(讀) 到 IICATAT ,IICATAT[7-6]還是表示的傳輸模式,IICATAT[5-4] == 0 1,發(fā)送停止信號

2、清除中斷掛起,SCL時鐘恢復,發(fā)出停止信號

3、延時,等待停止信號發(fā)出

3、 AT24C08 讀寫分析

1、寫過程

寫過程與2440芯片的里的寫流程相一致,按照流程寫就OK

2、讀過程

讀過程是由2440芯片里的一個寫流程加一個讀流程組合而成,其中寫流程結束沒有發(fā)出P信號,而是直接發(fā)出了S信號開始讀流程,也就是我為什么加了一道紅線的原因。

附上一份簡單的裸機程序,僅供參考:基于MINI2440

#include #include "s3c2440.h" void Delay(int time); #define WRDATA (1) #define RDDATA (2) typedef struct tI2C { unsigned char *pData; /* 數(shù)據(jù)緩沖區(qū) */ volatile int DataCount; /* 等待傳輸?shù)臄?shù)據(jù)長度 */ volatile int Status; /* 狀態(tài) */ volatile int Mode; /* 模式:讀/寫 */ volatile int Pt; /* pData中待傳輸數(shù)據(jù)的位置 */ }tS3C24xx_I2C, *ptS3C24xx_I2C; static tS3C24xx_I2C g_tS3C24xx_I2C; /* * I2C初始化 */ void i2c_init(void) { GPEUP |= 0xc000; // 禁止內(nèi)部上拉 /* * AT24C08 兩根線 I2CSCL I2CSDA 與 2440芯片相連 * 配置2440 GPECON GPE15 GPE14引腳為I2C功能 */ GPECON |= 0xa0000000; // 選擇引腳功能:GPE15:IICSDA, GPE14:IICSCL /* 開INT_IIC中斷 */ //INTMSK &= ~(BIT_IIC); /* bit[7] = 1, 使能ACK * bit[6] = 0, IICCLK = PCLK/16 * bit[5] = 1, 使能中斷 * bit[3:0] = 0xf, Tx clock = IICCLK/16 * PCLK = 50MHz, IICCLK = 3.125MHz, Tx Clock = 0.195MHz */ IICCON = (1<<7) | (0<<6) | (1<<5) | (0xf); // 0xaf //IICADD = 0x10; // S3C24xx slave address = [7:1] IICSTAT = 0x10; // I2C串行輸出使能(Rx/Tx) } void I_Write(unsigned int slvaddr, unsigned char addr, unsigned char data) { unsigned int ack; // 寫從地址 IICSTAT |= 0x1<<6;//主機寫模式 IICSTAT |= 0x1<<7; IICDS = slvaddr;//0xa0; //write slave address to IICDS IICCON&=~0x10; //clear pending bit IICSTAT = 0xf0; //(M/T start) while((IICCON & 1<<4) == 0);//udelay(10);//ack period and then interrupt is pending // 寫寄存器地址 IICDS = addr; IICCON&=~0x10; //clear pending bit while((IICCON & 1<<4) == 0);//udelay(10);//ack period and then interrupt is pending // 寫數(shù)據(jù) IICDS = data; IICCON&=~0x10; //clear pending bit while((IICCON & 1<<4) == 0);//udelay(10);//ack period and then interrupt is pending // 發(fā)出停止信號 IICSTAT = 0xD0; //write (M/T stop to IICSTAT) IICCON&=~0x10; //clear pending bit while((IICSTAT & 1<<5) == 1); } unsigned char I_Read(unsigned int slvaddr, unsigned char addr) { unsigned char data = 1; int ack; // 寫從地址 IICSTAT |= 0x1<<6;//主機寫模式 IICSTAT |= 0x1<<7; slvaddr = 0xA0; IICDS = slvaddr;//0xa0; //write slave address to IICDS IICCON&=~0x10; //clear pending bit IICSTAT = 0xf0; //(M/T start) while((IICCON & 1<<4) == 0);//udelay(10);//ack period and then interrupt is pending // 寫寄存器地址 IICDS = addr; IICCON&=~0x10; //clear pending bit while((IICCON & 1<<4) == 0);//udelay(10);//ack period and then interrupt is pending // 寫從地址(讀模式) slvaddr = 0xA1; IICSTAT &= ~(0x1<<6);//主機接受模式 IICSTAT |= 0x1<<7; IICDS = slvaddr; IICCON&=~0x10; //clear pending bit IICSTAT = 0xb0; //(M/R Start) while((IICCON & 1<<4) == 0);//udelay(10);//uart_SendByte('o');//ack period and then interrupt is pending:: // 讀數(shù)據(jù) data = IICDS; //IICCON&=~0x10; //clear pending bit IICCON = 0x2f; //清掛起狀態(tài),并設置無應答 while((IICCON & 1<<4) == 0);//udelay(10);//ack period and then interrupt is pending data = IICDS; //IICCON&=~0x10; //clear pending bit IICCON = 0x2f; //清掛起狀態(tài),并設置無應答 while((IICCON & 1<<4) == 0);//udelay(10);//ack period and then interrupt is pending IICSTAT = 0x90; IICCON = 0xaf; //IICCON &= ~0x10; //clear pending bit while((IICSTAT & 1<<5) == 1); return data; } 4、adapter驅(qū)動程序 這里,我們主要分析驅(qū)動里的發(fā)送核心算法,至于注冊中斷,IO內(nèi)存映射,設置寄存器不在討論。 static int xxx_i2c_xfer(struct i2c_adapter *adpap, struct i2c_msg *msg,int num) 這個算法函數(shù)的作用就是將上層封裝好的一些i2c_msg 進行解析,將數(shù)據(jù)寫入寄存器,發(fā)送出去。在設備驅(qū)動層,我們使用了類似i2c_smbus_write_byte 等函數(shù),類似的函數(shù)有很多,它們的作用就是封裝i2c_msg 結構(比如讀和寫的 msg 肯定不一樣,讀一個字節(jié)和讀多個字節(jié)也不一樣),然后調(diào)用 i2c_smbus_xfer_emulated->i2c_transfer,最終調(diào)用到我們的xxx_i2c_xfer函數(shù)進行傳輸。通過分析i2c_smbus_xfer_emulated函數(shù),我們可以了解i2c_msg是如何封裝的。下面,我們簡單分析一下,知道最上層想干什么,我們才能知道實現(xiàn)哪些底層的功能不是。 struct i2c_msg { __u16 addr; //從機地址 __u16 flags; __u16 len; // buf 里 有多少個字節(jié) __u8 *buf; // 本 msg 含有的數(shù)據(jù),可能是1個字節(jié),可有可能是多個字節(jié) }; 此函數(shù),省略了很多內(nèi)容,舉例分析而已~,細節(jié)請看源碼 static s32 i2c_smbus_xfer_emulated(struct i2c_adapter * adapter, u16 addr, unsigned short flags, char read_write, u8 command, int size, union i2c_smbus_data * data) { unsigned char msgbuf0[I2C_SMBUS_BLOCK_MAX+3]; unsigned char msgbuf1[I2C_SMBUS_BLOCK_MAX+2]; int num = read_write == I2C_SMBUS_READ?2:1; // 寫操作兩個Msg 讀操作一個msg 這和我們前面分析AT24c08是一致的 struct i2c_msg msg[2] = { { addr, flags, 1, msgbuf0 }, { addr, flags | I2C_M_RD, 0, msgbuf1 } }; msgbuf0[0] = command; // 從機地址右移1位得到的,比如AT24C08 為 0x50 switch(size) { case I2C_SMBUS_BYTE_DATA: // 單字節(jié)讀寫 if (read_write == I2C_SMBUS_READ) msg[1].len = 1; /* * 讀: * msgbuf0[0] = command * msg[1].len = 1 ,數(shù)據(jù)會讀到 msgbuf0[1] 里 */ else { msg[0].len = 2; msgbuf0[1] = data->byte; /* * 寫: * msgbuf0[0] = command * msgbuf0[1] = data->byte */ } break; } status = i2c_transfer(adapter, msg, num); } 上面代碼跟我們分析AT24C08的時候如出一轍,對于一個寫操作,我們只需要一個2440的寫流程對應于這里的一個Msg,然而對于讀操作,我們需要2440的兩個流程,對應于這里的兩個Msg。那么,我們底層控制器驅(qū)動需要做的工作就是,取出所有的Msg,將每一個Msg里buf里的數(shù)據(jù)發(fā)送出去,如果有下一個Msg, 那么再將下一個Msg里的buf發(fā)送完畢,最后發(fā)出P停止信號。還有一點,每發(fā)送一個Msg都要先發(fā)出S開始信號。 在看adapter程序之前,我們先來簡單思考一下,發(fā)出S開始信號之后,可能有以下3中情況: 1、當前msg.len == 0 ,如果有ACK直接發(fā)出stop信號。這種情況出現(xiàn)在,控制器枚舉設備的時候,因為它只發(fā)送S信號以及設備地址,不發(fā)送數(shù)據(jù)。 2、根據(jù)msg->flags 為 I2C_M_RD 等信息判斷讀寫,msg->flags 最低位為1表示讀,最低位為0表示寫。 #define I2C_M_TEN0x0010 /* this is a ten bit chip address */ #define I2C_M_RD0x0001 /* read data, from slave to master */

上一篇:i2c驅(qū)動程序全面分析,從adapter驅(qū)動程序到設備驅(qū)動程序

下一篇:Linux ARMv7中斷向量表搬移(2)

推薦閱讀最新更新時間:2025-04-17 02:02

設計資源 培訓 開發(fā)板 精華推薦

- 英飛凌微控制器:以全新實惠套件和強大開發(fā)環(huán)境為開發(fā)者提供支持

- iTOP-i.MX6開發(fā)板設備數(shù)驅(qū)動Menuconfig的用法

- 迅為IMX6ULL開發(fā)板Qt for Android搭建開發(fā)環(huán)境

- 迅為i.MX8M mini開發(fā)板Windots QT系統(tǒng)開發(fā)環(huán)境搭建

- 迅為IMX8MM開發(fā)板Yocto系統(tǒng)使用Gstarwmra(一)

- 迅為IMX8M mini開發(fā)板Linix系統(tǒng)修改默認屏幕

- iTOP-4412開發(fā)板支持4G以上文件系統(tǒng)擴展

- 迅為IMX8MM開發(fā)板Yocto系統(tǒng)設置開機自啟動

- 迅為IMX6Q開發(fā)板 Buildroot文件系統(tǒng)mqtt測試

- 通用AP3041升壓轉(zhuǎn)換器應用電路

- DK-DEV-5CEA7NES,Cyclone V E FPGA 開發(fā)板為低功耗開發(fā)和原型設計提供硬件平臺

- 基于梁山派電子物料收納盒

- AC-DC全橋整流電路

- AM1DM-0512SH60-NZ 12 Vout、1W 單路輸出 DC-DC 轉(zhuǎn)換器的典型應用

- AM437x 使用 LPDDR2 的低功耗掛起模式

- MIC4724 的典型應用:具有 6Vmax 輸入的 3A 2MHz 集成開關降壓穩(wěn)壓器

- +-35V功放開關電源

- EVAL-AD5370EB,使用 AD5370、40 通道、16 位、串行輸入、電壓輸出 DAC 的評估板

- 用于工業(yè)應用的 LT3973IDD-5 5V 降壓轉(zhuǎn)換器的典型應用

- AI算力狂飆下的能源困局,ST如何突圍?

- 韓國研究人員開發(fā)出耐火電池電解質(zhì)以防止熱失控

- “史上最嚴電池安全令”或引發(fā)產(chǎn)業(yè)第四次大洗牌

- 現(xiàn)代汽車發(fā)布新一代混動系統(tǒng),燃油效率提升45%

- 三星顯示將全面采用雙棧串聯(lián)技術提升車載OLED性能

- 禾賽科技計劃2026年推L3級智駕專用激光雷達“千厘眼”

- 寧德時代發(fā)布驍遙雙核電池:跨體系技術革新,續(xù)航超1000km

- 寧德時代發(fā)布全球首款800km續(xù)航12C超充磷酸鐵鋰電池

- 華為發(fā)布全液冷超充技術,15分鐘充電90%革新重卡市場

- 車規(guī)級MCU介紹

- 觀看福祿克計量校準視頻 參與調(diào)查問卷好禮送!

- 【已結束】R&S 直播【PCI Express Gen 3 一致性測試(含demo演示)】

- 瑞薩電子顛覆傳統(tǒng)理念的嵌入式開發(fā)平臺 Renesas Synergy™ 評估套件震撼來襲!答題即可免費申請!

- 是德科技有獎直播:灣區(qū)圓桌派-穿越頻譜壁壘:毫米波技術的創(chuàng)新之路

- 是德科技第二屆示波器感恩月之買一送一

- 話說我接觸的ADI實驗室電路“評估板”

- 安森美半導體移動與可穿戴設備解決方案下載有禮!

- Nexperia ESD 應用手冊|讀 ESD 干貨答題贏好禮

- Microchip 直播|利用motorBench®開發(fā)套件高效開發(fā)電機磁場定向控制方案

- 【EEWORLD第四十一屆】2012年08月社區(qū)明星人物揭曉!

軟件調(diào)試 第2版 卷2 Windows平臺調(diào)試 (張銀奎)

軟件調(diào)試 第2版 卷2 Windows平臺調(diào)試 (張銀奎) CVPR 2023論文匯總:高效和可擴展視覺 Efficient and Scalable Vision

CVPR 2023論文匯總:高效和可擴展視覺 Efficient and Scalable Vision CAN總線輕松入門與實踐

CAN總線輕松入門與實踐 7800302GX

7800302GX

京公網(wǎng)安備 11010802033920號

京公網(wǎng)安備 11010802033920號