隨著示波器用戶對速度更快、功耗更低和體積更小的存儲器的需求與日俱增,雙倍數據速率(DDR)存儲器技術在過去五年里得到了巨大的發展。

DDR4 的含義是具有雙倍數據速率的第四代 SDRAM 存儲器。與 DDR3 相比,DDR4 的數據傳輸帶寬大幅增加,而且在速度、密度和功率等方面都超越以往。這些技術進步推動企業級應用、微型服務器應用和平板電腦應用的性能和能效進一步提高,讓設計人員可以設計芯片更小、功耗更低、散熱更少的器件。

DDR4 存儲器的體系結構整合了 DDR3(雙向 DQS)和類似 GDDR5 的數據總線(CRC 和數據誤碼檢測功能)兩方面的關鍵特性。但 DDR4 信號也有一些特性與上一代 DDR 解決方案截然不同。這些關鍵差異促使新的測試方法問世。

信號完整性的問題

信號完整性對于存儲器系統的可靠運行至關重要。測試信號完整性,首先應從物理層開始,數據在這一層通過時鐘上升沿和下降沿進行傳輸。但是在測試 DDR4 存儲器的物理層時遇到了一些新的挑戰。

按照電子器件工程聯合會(JEDEC)標準的要求,在實施電子、時序和眼圖測試時都需要執行輸入和輸出測量,其中包含大量測試操作以確保存儲器系統正常運行,不會發生錯誤。DDR4 的速度提升還要求通過分離讀寫周期來測量 AC 時序參數。

存儲器速度的提高,也導致隨機抖動爆增。DDR4 是第一款速度超快而必須將抖動控制在規定范圍內的 DRAM。過多的抖動會減少數據有效窗口,所以必須明確定義 DDR4 的數據有效窗口。

DDR4 器件開發人員所關注的另一個問題是互操作性。其最終目標是保證存儲器系統的通用功能,同時提高效率和生產力。唯有清晰地了解 DDR4 規范的測試要求(例如,存儲器時序、眼圖測量和抖動)和測試過程(例如,正確的探測和仿真協議),您才能恢復裕量,縮短芯片/系統的設計周期、降低成本并加快產品上市速度。最終目標是保證存儲器系統具備通用功能,且達到更高能效和生產效率。

什么是抖動?

抖動是指信號的時序事件偏離其理想位置的現象。

DDR4測試要求

前幾代 DDR 存儲器的時序規范基于多種風險假設,其中最大的假設是,只要數據設置和保持時間符合規范,就可以實現完美的數據捕獲。DDR2 和 DDR3 的數據速率較慢且裕量較大,其規范假設隨機抖動可忽略不計且比特誤碼率(BER)為零。當然,它實際上并不為零。對于時鐘抖動,測量 10,000 個周期的時鐘周期,其誤碼率將為 1e-4,因而可以認為它足夠接近零。DDR2 和 DDR3 較低的數據傳輸速度使得這些假設可以成立,因為在系統發現不合格結果之前存在足夠的裕量。

DDR4 的數據速率更快,這會降低裕量,隨機抖動可能會快速關閉數據眼圖,這意味著誤碼率會增加。如果不加以控制,有可能會產生嚴重的系統可靠性問題、延長設計時間、減緩產品上市時間并增加設計周期的成本。然而,DDR4 測試要求可以正面地解決這些問題,保障可靠性并降低成本。

將捕獲的波形數據顯示為實時眼圖(RTE),可以深入了解串行數據信號中的抖動。眼圖基本上是數字化比特的疊加,顯示比特何時有效(高或低)。它提供了描述系統物理層特征質量的合成圖像,并使峰峰值邊緣抖動和噪聲得以具體顯示。

實時眼圖測試執行眼高和眼寬測量,檢查信號完整性并預估數據有效窗口。然而,僅測量數據眼圖并不能完全了解數據有效窗口或預估比特誤碼率。目前,DDR4 規范的信號完整性測量的是最差情況下的時間裕度(tDIVW)和電壓(vDIVW)。

眼圖模板測試是最重要的物理層測量之一,可用于測試總體信號完整性。從總體抖動可以推導出與眼圖模板相關的最小時間和最小電壓的裕量。如果定義的 BER 很大(或者如果存在少量數據),就可以直接執行測量。如果測試的 BER 很小,那么測量數萬億個單位間隔(UI)就會花費太多時間。

眼圖模板測試可確保數據眼圖不會超過可能發生抖動(和誤碼)的模板邊界。除此之外,它可以通過 tDIVW 測量結果(圖 1)報告最小裕量(模板四個角的四個時序點)。

圖 1. 眼圖模板測試可以確保信號不會超過模板邊界(在邊界上可能發生抖動和誤碼)。

眼圖測試

–可以測量數據眼高和眼寬

–用戶還可以根據器件規范定義自己的眼圖模板

–如果眼圖不符合模板,那么一致性應用軟件可以報告不合格狀態

DDR4 規范考慮了抖動和 BER 的關鍵作用。計算抖動 BER 測量結果很重要,它可以統計測量總體抖動(確定性抖動+隨機抖動),了解設計的數據有效窗口結果和可能出現錯誤的概率。

除了規范測試,采用正確的測試過程和方法也是至關重要的。例如,示波器探頭的正確放置會影響一致性測試結果以及設計裕量的準確表征和測試。對于 JEDEC 規范,最佳探測點位于 DRAM 封裝的球上(不在傳輸線或通道上,也不在存儲器控制器上)。

仿真是測試過程中的另一個重要卻經常被忽略的步驟。隨著總線速度的提高以及獲得盡量多裕量的需求,仿真過程可以很大程度地幫助減少設計周期和成本。

例如,仿真有助于確保系統能夠容忍內插器的負載效應。這一步驟評測所測量的帶寬/頻率響應,確保內插器不會斷開總線。

最后,是德科技與 JEDEC 組織密切合作,以確保其測試和測量解決方案與 JEDEC 標準的測試和測量規范保持高度一致。

圖 2. 然后將具有適當負載效應的仿真設計與原型的實際掃描結果進行比較,確定系統正常運行。

技術洞察:計算總體抖動

確定性抖動(DJ)通常是有界而可預測的,可以與數據流相關聯,例如符號間干擾和占空比失真。隨機抖動(RJ)屬于高斯分布并且是無界的。與任何高斯分布一樣,隨著總量的增加,分布的峰-峰值也會增加。因此,總體抖動(TJ)等于確定性抖動 DJ 加上隨機抖動 RJ 與 BER 的乘積。了解抖動的組成和來源可以幫助設計人員降低設計中抖動的發生率,確保更好的數據性能。

物理層 DDR4 測試的解決方案

準確執行測試的三個步驟:

選擇合適的探頭并把它置于正確的位置

選擇能夠執行適當應用分析的示波器

使用符合 JEDEC 標準的自動一致性測試應用程序

1. 選擇合適的探頭并把它置于正確的位置

對于采用 DDR4 存儲器的計算機系統設計,有幾種探測方法可以訪問用于測試的存儲器系統。第一種探測方法適用于計算機系統有內存插槽/連接器,可以插入DIMM 或 SODIMM 的場景。對于此類配置,訪問信號的最簡單方法是使用插槽內插器(圖 3)。

圖 3. SODIMM 插槽內插器

插槽內插器將所有命令信號路由到電纜,該電纜能夠代替 MSO 電纜而直接連接到混合信號示波器(MSO)的輸入端。訪問數據選通信號(DQS)和輸出數據(DQ)時,探頭前端可以焊接到插槽內插器上并連接到模擬通道(圖 4)。這樣就可以查看 SODIMM 的 16 個數字通道以及通過模擬通道傳輸的 DQS 和 DQ 信號。

圖 4. 使用焊入式探頭前端可以訪問路由到示波器模擬通道的 DQS 和 DQ 信號。在本例中,我們使用的探頭前端是 E2677A。

另一種選擇是 DDR4 BGA 探測,它適用于測試嵌入式系統(或 DIMM 配置)。對 DDR4 而言,BGA 內插器的設計目的是提供訪問所有信號的途徑,以便在表征所有信號(數據、地址、控制、命令、選通和時鐘)時實現最大的靈活性。使用這種探測方法時,需要將 BGA 內插器焊接在 DRAM 和電路板之間。連接示波器的焊點位于 BGA 頂部(圖 5)。

圖 5. Keysight DDR BGA 內插器。通過內插器周圍的示波器焊點訪問信號。

如果空間特別狹小(特別是在 DIMM 配置中),可能需要轉接器將內插器從電路板上架高,這樣它就不會干擾任何相鄰的元器件(圖 6)。在這種情況下,轉接器將焊接在內插器的底部。

圖 6. DDR BGA 內插器配有一個轉接器,用于在表面積較小的區域內架高內插器。

定制內插器

如果您需要一款內插器,而我們現有的設計無法滿足您的需求,那么我們的設計團隊能夠與您合作創建定制解決方案。請與是德科技合作以啟動這一流程,或訪問:www.keysight.com/find/contactus。

2. 選擇能夠執行適當應用分析的示波器

確定探測協議之后,下一個關鍵的考慮因素是選擇測試設備。盡管存儲器技術的 BER 規范才剛制定,但這種測試已然成熟運用于高速設計,并得到相應測量工具(如示波器)的支持。使用具有先進測量分析功能的示波器非常重要,這些功能包括去嵌入、實時眼圖測量、混合模擬和數字信號;以及交叉參照仿真設計等。

MSO 示波器是一種能夠同時顯示和分析數字和模擬信號的儀器。MSO 的一個優勢是能夠分離讀寫數據。用戶可以將命令總線、行地址選通(RAS)、列地址選通(CAS)、寫入激活(WE)、片選(CS)和時鐘信號連接到數字通道,使示波器根據這些信號中的任意信號或信號組合觸發讀命令或寫命令。它可以分離相應的數據并執行電子和時序測試。MSO 還允許測試人員查看命令協議的流程,檢測協議是否違規。

選擇示波器時,必須要了解它與其他設計和測試工具如何整合。是德科技利用其作為世界知名電子測量公司的獨特地位,精心構建先進的 EDA(軟件仿真)工具和示波器。當在 DDR4 設計的最后階段運行傳統的電子和時序規范時,是德科技的工具套件提供了獨特的優勢,能夠對候選版本中的仿真波形和物理原型的波形測量結果執行完全相同的一致性測試。換句話說,仿真波形可以導入示波器中,與從物理原型獲得的波形進行比較。

仿真過程可以顯著減少設計的迭代次數和成本。每次執行探測時,都會給系統增加額外負載。仿真該負載可確保內插器不會破壞總線或產生任何未知負載。Keysight W2351 DDR4 一致性測試臺可用于仿真負載效應并生成去嵌入文件,從而消除探測效應并使用示波器進行測量(關于去嵌入的詳細信息,請參閱下一頁的步驟 3),這樣就可以真實地將您仿真的設計與原型進行比較。

Keysight Infiniium V 系列示波器

Keysight Infiniium V 系列示波器針對高速 DDR 存儲器測量進行了優化。V 系列提供業界較低的本底噪聲和抖動測量本底以及較高的有效位數(ENOB),因而成為發射機信號完整性測量的理想工具。提供從 8 GHz 至 33 GHz 的各種型號,并可升級其帶寬以滿足您未來的需求。它與 InfiniiMax III 和 III+ 探測系統結合使用,可以提供更精確的測量,滿足更苛刻的設計裕量要求。另外,它還提供 16 個數字通道,時間分辨率高達 50 ps。此外,借助是德科技先進設計系統(ADS)和 DDR4 軟件,您可以直接將仿真結果與示波器軟件測得的實際特征相關聯。

需要詢問示波器供應商的問題:

我可以交叉觸發和測量數字和模擬通道嗎?

示波器是否具有去嵌入功能?

它是否具有實時眼圖測量功能?

我可以將它交叉引用到我的仿真設計中嗎?

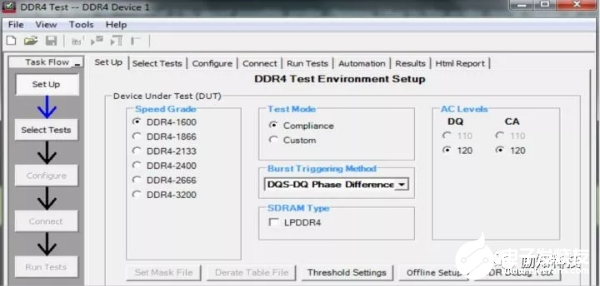

3.使用符合 JEDEC 標準的自動一致性測試應用程序

測試解決方案的最后一個組成部分是示波器軟件。利用 DDR4 一致性測試應用軟件(例如Keysight N6462A DDR4 電氣一致性測試軟件),您可以使用日常用于調試的示波器,按照 JEDEC 規范執行自動存儲器測試和裕量分析。每次測試時,該應用軟件都會自動配置示波器,使其可以提供有效結果。它還包括裕量分析,指示您的器件距離各項規范的合格標準有多遠。

一致性應用軟件還應具有某種“自定義”模式,可以涵蓋包括眼圖分析、模板測試和振鈴在內的關鍵測量。這些測量對表征 DDR4 器件至關重要。

Keysight DDR4 一致性測試應用軟件可測試 JEDEC SDRAM 規范中規定的時鐘、電氣和時序參數。該應用軟件可以幫助您使用 Keysight Infiniium 示波器測試所有 DDR4 和 LPDDR4(低功耗)器件的一致性。

是德科技的應用軟件還可以提供詳細的報告,包括用屏幕快照顯示的最差情況值,以及根據規范確定的測量結果的合格/不合格狀態。它還可以計算距離規范合格線的裕量。用戶可以增加運行次數,收集更多數據進行統計分析。統計報告將顯示測試的最小值、最大值和標準差。這些數據在比較 DRAM 供應商或不同客戶的測試結果時特別有用。

Keysight DDR4 電氣一致性測試軟件報告包括:

1.利用屏幕快照顯示的最差情況值

2.合格/不合格狀態以及距離該標準的裕量

3.多次試運行結果

4.包括最小值、最大值和標準差的統計報告

技術洞察:InfiniiSim

Keysight InfiniiSim 波形轉換工具套件提供更靈活、更準確的方法,來顯示數字串行數據鏈路中任意處的波形。高度可配置的系統建模能夠簡單快速地幫你消除多余通道元素的有害影響,仿真插入了通道模型的波形,查看物理上無法探測位置的波形,補償探頭和其他電路元件的負載效應。最終目標是在根據規范進行測試或執行表征工作時獲得更多裕量。

Keysight DDR4 電氣一致性測試軟件的優勢:

是德科技積極參與 JEDEC 組織的各項工作 — 在 DDR4/LPDDR4 BER 測試方法上做出了關鍵貢獻

比競爭對手更多的測試覆蓋率

DDR4 一致性測試解決方案的一站式商店(軟件+ BGA 內插器)

通過 W2351 一致性測試臺軟件交叉引用并仿真運行

Infiniisim 波形轉換工具套件

總結

DDR4 的速度要求以新的方式定義和測量關鍵的 AC 時序參數(例如數據輸入有效窗口的時序和電壓)。示波器配備的探測分析工具與自動一致性測試相結合,可以確保測試結果的可重復性和可靠性。

設計人員若想縮短學習時間,盡快掌握新一代測試與測量協議的知識,那么最好考慮與積極參與 JEDEC 標準委員會工作的測試工具廠商合作。通過密切的協作和溝通,設計人員可以找到更新、更好的一致性測試解決方案。這對于新發布的技術尤其重要,因為其規范和測量方法仍然處于討論過程中。

Keysight DDR4 眼圖輪廓測試方法目前得到 JEDEC 的采納,用于 DDR4 標準化工作。是德科技還是一家在 DDR 芯片開發所有階段均提供硬件和軟件解決方案的測試與測量公司。從仿真到調試,從驗證到一致性測試,是德科技的解決方案都發揮了重要作用。

任何從 DDR 存儲器設計的技術人員都面臨著在不斷縮小的封裝中實現更快存取速度和更低功耗的持續壓力。在產品設計階段盡早洞察您的設計,可以快速采取糾正措施,確保您的產品達到質量、互操作性和上市時間等目標。成功的設計取決于效率以及縮短設計周期,控制設計成本。幸運的是,今天有許多工具可以幫助您實現這一目標。

上一篇:差分信號的應用優勢及差分探頭的種類及作用介紹

下一篇:淺談模擬示波器觸發模式和功能

推薦閱讀

史海拾趣

隨著電子行業的快速發展,BOPLA意識到傳統的電子元件已經無法滿足市場的需求。于是,公司投入大量資源進行技術研發,成功推出了一系列具有創新性的電子元件產品。這些產品不僅性能優異,而且具有更高的可靠性和穩定性,贏得了市場的廣泛好評。

隨著公司規模的不斷擴大和業務的快速發展,智浦欣公司意識到,必須加強內部管理和人才培養才能確保公司的持續健康發展。于是,公司引進了一套先進的管理體系和人才培養計劃。在管理體系方面,公司建立了完善的組織架構和業務流程,提高了工作效率和協同能力;在人才培養方面,公司注重員工的個人發展和職業規劃,提供了多樣化的培訓和學習機會,激發了員工的工作熱情和創新能力。

隨著技術的不斷進步和市場需求的日益增長,智浦欣公司意識到,只有不斷創新和突破,才能在激烈的市場競爭中立于不敗之地。于是,公司加大了對研發團隊的投入,引進了一批國內外頂尖的模擬器件和混合信號設計人才。經過數月的努力,團隊成功研發出了一款具有高性價比的WLED驅動器產品,該產品以其卓越的性能和穩定的質量贏得了客戶的廣泛好評。隨后,公司又相繼推出了多款具有競爭力的新產品,進一步鞏固了其在消費類電子市場的地位。

隨著全球對環保和可持續發展的重視程度不斷提高,智浦欣公司也積極響應這一趨勢,將綠色環保理念融入到公司的經營和發展中。公司采用環保材料和綠色生產工藝,減少了對環境的污染和破壞;同時,公司還積極參與公益事業和社會活動,推動社會和諧發展。這些舉措不僅提升了公司的社會責任感和公信力,還為公司贏得了更多的客戶支持和合作伙伴。

以上五個故事是基于對智浦欣公司在電子行業發展中可能經歷的情景進行的虛構敘述。雖然這些故事并非真實發生的事件,但它們能夠反映出智浦欣公司在發展過程中可能面臨的挑戰、機遇和策略選擇。

為了進一步擴大市場份額,Catalyst公司積極實施國際化戰略。公司通過與國外知名企業的合作與交流,引進先進的技術和管理經驗,不斷提升自身的競爭力。同時,Catalyst還積極參加國際電子展會和論壇,展示公司的最新產品和技術成果,吸引了眾多國際客戶的關注。通過國際化戰略的拓展,Catalyst成功打開了海外市場的大門,為公司的長遠發展奠定了堅實的基礎。

為了進一步擴大市場份額,Catalyst公司積極實施國際化戰略。公司通過與國外知名企業的合作與交流,引進先進的技術和管理經驗,不斷提升自身的競爭力。同時,Catalyst還積極參加國際電子展會和論壇,展示公司的最新產品和技術成果,吸引了眾多國際客戶的關注。通過國際化戰略的拓展,Catalyst成功打開了海外市場的大門,為公司的長遠發展奠定了堅實的基礎。

|

DCDC的意思是直流變(到)直流(不同直流電源值的轉換),只要符合這個定義都可以叫DCDC轉換器,包括LDO。但是一般的說法是把直流變(到)直流由開關方式實現的器件叫DCDC。 LDO是低壓降的意思,這有一段說明:低壓降(LDO ...… 查看全部問答∨ |

|

|

本人搜集到的一篇很好的文章,因此轉載給各位大蝦,希望對工程師們有所幫助: 何靠與電打交道來謀生的人很快都會對任何“帶電”的物體生出理性的敬意,哪怕是“帶電”的機會很小。然而,需要按時完成一項工作或者使某個關鍵設備恢復聯機的緊迫壓力 ...… 查看全部問答∨ |

|

|

error C2065: \'GetRunningObjectTable\' : undeclared identifier error C2065: \'CreateItemMoniker\' : undeclared identifier 我用的是EVC 4.0+SP4… 查看全部問答∨ |

STM32的驅動庫好用嗎?效率高嗎?優化的嗎?準備上STM32 N多年沒買過開發板了,也沒用過仿真器了。都是用軟件編譯調試好,直接ISP,然后通過串口命令開啟調試信息的輸出。 昨天買了塊STM32F103全功能型開發板,他們的辦事效率真低(深圳到廣州通常當 ...… 查看全部問答∨ |

|

求IAR Embedded Workbench for MCS-51 完整版 各位高手,小弟求IAR Embedded Workbench for MCS-51完整版,有哪位高人有,能否分享一下。我的郵箱jinghongchen@126.com… 查看全部問答∨ |

|

|

在Project Navigator中使用集成的PlanAhead功能只支持四種模式,如下圖所示: 下載 (83.89 KB) 14 分鐘前 1. 我要通過PlanAhead實現分區(Partition)設計,貌似這種集成的PlanAhead不支持啊,對么?在相應的右鍵菜單中沒有se ...… 查看全部問答∨ |

最近在看STM8L的spc發現中斷優先順序實在不太明白。中斷優先順序分為兩個暫存器,一個為CC暫存器的 I0 和 I1和ITC_SPRX暫存器,但我不明白的昰既然ITC_SPRX已經設定了個向量中斷的優先順序,那CC暫存器設定是為了甚麼呢,請哪位大大可以幫幫我,謝 ...… 查看全部問答∨ |

X9317WV8Z

X9317WV8Z

京公網安備 11010802033920號

京公網安備 11010802033920號