本電路為寬帶直接變頻發射機模擬部分的完整實現方案(模 擬基帶輸入、RF輸出)。通過使用鎖相環(PLL)和寬帶集成 電壓控制振蕩器(VCO),本電路支持500 MHz至4.4 GHz范圍 內的RF頻率。對來自PLL本振(LO)進行諧波濾波,確保提 供出色的正交精度、邊帶抑制和低EVM。

?

?

低噪聲、低壓差調節器(LDO)確保電源管理方案對相位噪 聲和EVM沒有不利影響。這種器件組合可以提供500 MHz 至4.4 GHz頻率范圍內業界領先的直接變頻發射機性能

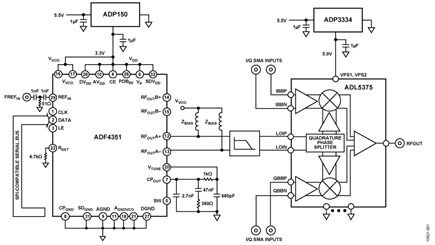

圖1所示電路使用完全集成的小數N分頻PLL IC ADF4351和寬帶發射調制器 ADL5375。ADF4351向發射正交調制器ADL5375提供LO信號,后者將模擬I/Q信號上變頻為RF信號。兩個器件共同提供寬帶基帶I/Q至RF發射解決方案。ADF4351采用超低噪聲3.3 V ADP150調節器供電,以實現最佳LO相位噪聲性能。ADL5375則采用5 V ADP3334LDO供電。ADP150LDO的輸出電壓噪聲僅為9 μV rms,有助于優化VCO相位噪聲并減少VCO推壓的影響(等效于電源抑制)。

需要對ADF4351 RF輸出進行濾波,以衰減諧波水平,使ADL5375正交產生模塊的誤差最小。依據測量和仿真得知,奇次諧波對正交誤差的貢獻大于偶次諧波;如果將奇次諧波衰減至?30 dBc以下,則可以實現?40 dBc或更好的邊帶抑制性能。ADF4351數據手冊給出了其二次諧波(2H)和三次諧波(3H)水平,如表1所示。

為使三次諧波低于?30 dBc,大約需要衰減20 dB。

| ?諧波成分 |

?數值(dBc) |

?描述 |

| ?第二 |

?-19 |

?基波VCO輸出 |

| ?第三 |

?-13 |

?基波VCO輸出 |

| ?第二 |

?-20 |

?分頻VCO輸出 |

| ?第三 |

?-10 |

?分頻VCO輸出 |

本電路提供四種不同的濾波器選項,以適應四個不同的頻 段。這些濾波器設計采用100 Ω差分輸入(ADF4351 RF輸出經適當匹配)以及50 Ω差分輸出(ADL5375 LOIN差分阻抗)。并采用切比雪夫響應,以獲得最佳濾波器滾降,但通帶內紋波會增多。

濾波器原理圖如圖3所示。這種拓撲結構十分靈活,既可以使用全差分濾波器,使器件數量最少,也可以對各路輸出使用一個單端濾波器,或者綜合運用以上二者。我們發現,對于較高頻率(>2 GHz),兩個單端濾波器的串聯電感值是全差分濾波器電感值的兩倍,因而器件寄生效應的影響得以減小,可提供最佳性能。對于較低頻率(<2 GHz),全差分濾波器足以滿足需要。

ADF4351 輸出匹配包括ZBIAS上拉電阻,電源節點的去耦電容也起到一定的作用。為實現寬帶匹配,建議使用阻性負載(ZBIAS = 50 Ω),或者將一個阻性負載與ZBIAS的電抗性負載并聯。后者提供的輸出功率稍高,具體取決于所選的電感。請注意,可以將并聯電阻作為差分元件(即100 Ω)放置在C1c位置上,以最大程度減少電路板占位空間(見表2中的B型濾波器)。

將濾波器設計成截止頻率約為目標頻段中最高頻率的1.2至1.5倍。該截止頻率允許設計留有一定余量,因為通常截止頻率會由于寄生效應而低于設計值。印刷電路板(PCB)寄生效應可以在電磁(EM)仿真工具中進行仿真,以提高精度。

?

| ?頻率范圍(MHz) |

?ZBIAS |

?L1 (nH) |

?L2 (nH) |

?C1a (pF) |

?C1c (pF) |

?C2a (pF) |

?C2c (pF) |

?C3a (pF) |

?C3c (pF) |

| ?500至1300(A 型濾波器) |

?27 nH||50? |

?3.9 |

?3.9 |

?DNI |

?4.7 |

?DNI |

?5.6 |

?DNI |

?3.3 |

| ?850至2450(B型濾波器) |

?19 nH||(100Ω,位置C1c) |

?2.7 |

?2.7 |

?3.3 |

?100? |

?4.7 |

?DNI |

?3.3 |

?DNI |

| ?1250至2800(濾波器類型C) |

?50? |

?0? |

?3.6 |

?DNI |

?DNI |

?2.2 |

?DNI |

?1.5 |

?DNI |

| ?2800至4400(濾波器類型D) |

?3.9 nH |

?0? |

?0? |

?DNI |

?DNI |

?DNI |

?DNI |

?DNI |

?DNI |

從表2可以看出,在1250 MHz以下的較低頻率時,需要一個五階濾波器。對于1.25 GHz至2.8 GHz的頻率,三階濾波器便足夠。對于2.8 GHz以上的頻率,由于此時諧波水平非常低,足以滿足邊帶抑制要求,因此無需濾波。

?

?

對于使用B型濾波器(800 MHz至2,400 MHz)的電路,其邊帶抑制性能與頻率的關系如圖4所示。此次掃描的測試條件如下:

EVM衡量數字發射機或接收機的性能質量,反映幅度和相位誤差所導致的實際星座點與理想位置的偏差(見圖5)。

表3給出了有濾波器和無濾波器兩種情況下的EVM測量結果。本例中,基帶I/Q信號是利用3GPP測試模型4,使用Rhode & Schwarz AMIQ I/Q調制發生器,通過差分I和Q模擬輸出產生。另外還使用了B型濾波器。圖6為EVM測試設置的框圖。為了進行比較,還測量了ADF4350。ADF4351由于帶內PLL噪聲性能改善產生較低的EVM可參見表3。其他改善EVM的因素有:ADF4351較低的鑒頻鑒相器(PFD)雜散水平。

| ?頻率(MHz) |

?ADF4350復合EVM,無LO濾波 |

?ADF4350復合EVM,有LO濾波,濾波器B |

?ADF4351復合EVM,有LO濾波,濾波器B |

| ?2140 |

?3.27% |

?1.31% |

?1.02% |

| ?1800 |

?1.46% |

?1.13% |

?0.95% |

| ?900 |

?10.01% |

?1.03% |

?0.96% |

?

以差分方式驅動ADL5375 LO輸入,除了可以改善邊帶抑制和EVM之外,還具有性能優勢。與單端LO驅動相比,這一優勢提高了調制器輸出OIP2性能2 dB至5 dB。請注意,多數外部VCO僅提供單端輸出,因此 ADF4351采用差分輸出優于使用外部VCO。

圖7顯示使用850 MHz至2450 MHz濾波器(B型濾波器)的邊帶抑制結果。

?

有關本電路筆記的完整設計支持包,請參閱 http://www.analog.com/CN0285-DesignSupport.

解決方案框圖

!注意:請使用瀏覽器自帶下載,迅雷等下載軟件可能無法下載到有效資源。

| 器件 | 類型 | 描述 | 數據手冊 |

|---|---|---|---|

| ADP3334 | 正線性穩壓器(LDO) | 高精度、低IQ、500 MA ANYCAP?可調低壓差穩壓器 | 點擊下載 |

| ADL5375 | I/Q調制器 | 400 MHz 至6 GHz 寬帶正交調制器 | 點擊下載 |

| ADP150 | 正線性穩壓器(LDO) | 超低噪聲、150 mA CMOS線性調節器 | 點擊下載 |

| ADF4351 | 整數 N PLL | 集成VCO的寬帶頻率合成器 | 點擊下載 |

歡迎加入EEWorld參考設計群,也許能碰到搞同一個設計的小伙伴,群聊設計經驗和難點。 入群方式:微信搜索“helloeeworld”或者掃描二維碼,備注:參考設計,即可被拉入群。 另外,如您在下載此設計遇到問題,也可以微信添加“helloeeworld”及時溝通。

EEWorld Datasheet 技術支持